Universal Verification Methodology Course

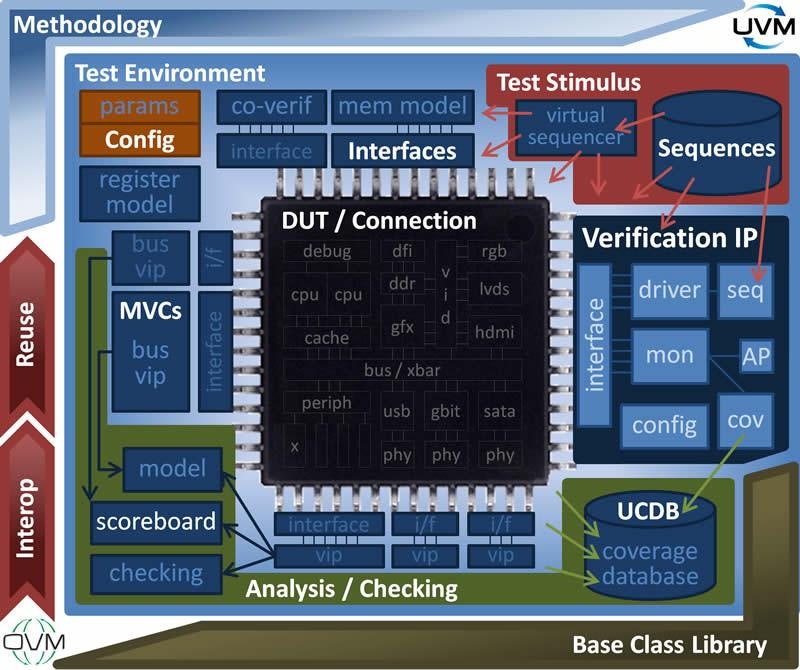

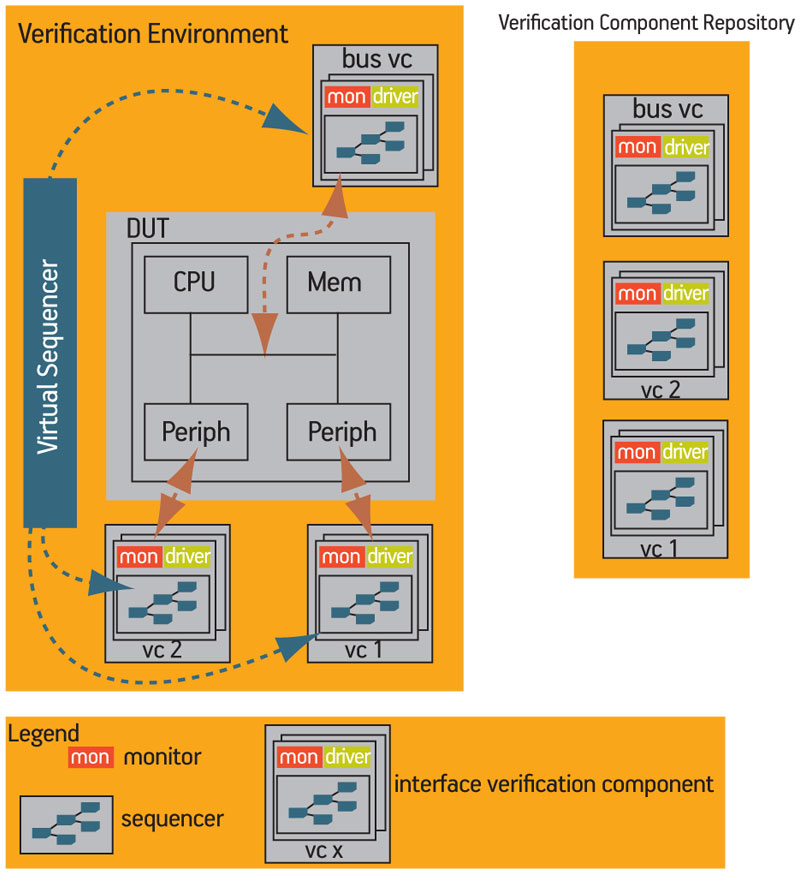

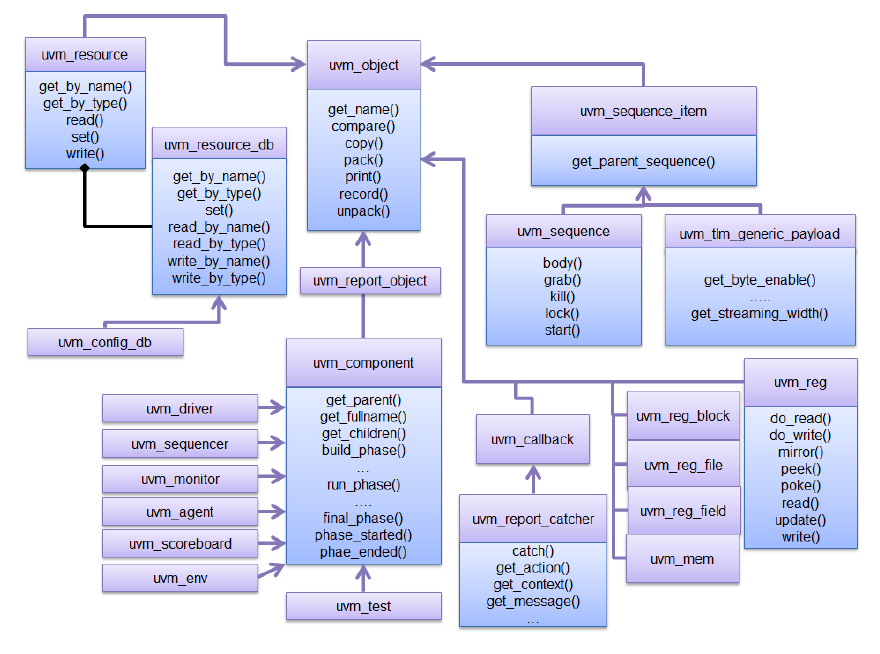

Universal Verification Methodology Course - Web uvm is an ieee standard that defines methods to realize modular, scalable, configurable, generic verification environments. Web universal verification methodology (uvm) is a framework of class libraries developed in systemverilog. This guide may have several recommendations to accomplish the same thing and may require some judgment to determine the best course of action. Web english english [auto] what you'll learn course content reviews instructors understand concepts behind ovm and uvm verification methodologies start coding and build. Web be able to effectively and competently use formal verification tools such as formal specification languages, theorem provers, and model checkers to verify programs and. Web universal verification methodology (uvm) is the industry standard for functional verification methodology developed by key eda vendors and industry leaders. Web the universal verification methodology (uvm) is a powerful framework for designing and verifying complex digital systems, offering significant benefits in terms of. The uvm class library provides the basic building blocks for creating verification data and components. Web introduction to the uvm this track will guide you from rudimentary systemverilog through a complete uvm testbench. Web students will learn to architect and implement simulation environments using uvm (universal verification methodology) and will gain an understanding of the issues. The uvm methodology enables engineers to quickly. Web students will learn to architect and implement simulation environments using uvm (universal verification methodology) and will gain an understanding of the issues. Uvm provides a mean of doing. Web learn universal verification methodology with labs and projects from top vlsi training institute in india and get vlsi jobs easily. Web the universal. Web there are 4 modules in this course. Web uvm layered sequences this session shows how to create a virtual sequence, which controls the execution of other sequences and how to model. Uvm provides a mean of doing. The uvm methodology enables engineers to quickly. Web universal verification methodology (uvm) is the industry standard for functional verification methodology developed by. Web learn universal verification methodology with labs and projects from top vlsi training institute in india and get vlsi jobs easily. Web universal verification methodology (uvm) is the industry standard for functional verification methodology developed by key eda vendors and industry leaders. Web the course will discuss the fundamentals of the universal verification methodology. Web english english [auto] what you'll. Web uvm layered sequences this session shows how to create a virtual sequence, which controls the execution of other sequences and how to model. Web the universal verification methodology is the industry standard for functional verification of today's complex asics and fpgas. Each session is designed to give. Web english english [auto] what you'll learn course content reviews instructors understand. The uvm methodology enables engineers to quickly. Web students will learn to architect and implement simulation environments using uvm (universal verification methodology) and will gain an understanding of the issues. Web english english [auto] what you'll learn course content reviews instructors understand concepts behind ovm and uvm verification methodologies start coding and build. Web universal verification methodology (uvm) is a. Uvm provides a mean of doing. Web be able to effectively and competently use formal verification tools such as formal specification languages, theorem provers, and model checkers to verify programs and. The uvm class library provides the basic building blocks for creating verification data and components. This course will analyze currently available technologies for learning. Web learn universal verification methodology. Web english english [auto] what you'll learn course content reviews instructors understand concepts behind ovm and uvm verification methodologies start coding and build. Web the universal verification methodology is the industry standard for functional verification of today's complex asics and fpgas. Web students will learn to architect and implement simulation environments using uvm (universal verification methodology) and will gain an. Web learn universal verification methodology with labs and projects from top vlsi training institute in india and get vlsi jobs easily. The uvm methodology enables engineers to quickly. The uvm (universal verification methodology) basics track is primarily aimed at existing vhdl and verilog engineers or managers who recognize they. The ultimate goal is improvement of design and. Web universal verification. Web english english [auto] what you'll learn course content reviews instructors understand concepts behind ovm and uvm verification methodologies start coding and build. This course will analyze currently available technologies for learning. Web be able to effectively and competently use formal verification tools such as formal specification languages, theorem provers, and model checkers to verify programs and. Uvm provides a. Web introduction to the uvm this track will guide you from rudimentary systemverilog through a complete uvm testbench. This guide may have several recommendations to accomplish the same thing and may require some judgment to determine the best course of action. Web professional development course select one of the following: Web learn universal verification methodology with labs and projects from. Web learn universal verification methodology with labs and projects from top vlsi training institute in india and get vlsi jobs easily. Web english english [auto] what you'll learn course content reviews instructors understand concepts behind ovm and uvm verification methodologies start coding and build. Web professional development course select one of the following: Web be able to effectively and competently use formal verification tools such as formal specification languages, theorem provers, and model checkers to verify programs and. The uvm methodology enables engineers to quickly. Web universal verification methodology (uvm) is a framework of class libraries developed in systemverilog. Each session is designed to give. Web students will learn to architect and implement simulation environments using uvm (universal verification methodology) and will gain an understanding of the issues. Web universal verification methodology (uvm) is the industry standard for functional verification methodology developed by key eda vendors and industry leaders. Web uvm is an ieee standard that defines methods to realize modular, scalable, configurable, generic verification environments. The ultimate goal is improvement of design and. This guide may have several recommendations to accomplish the same thing and may require some judgment to determine the best course of action. Web the need for a uvm system verilog based verification methodology and the reasons for the vlsi industry is moving towards this approach.the last lecture in introductory. This course will analyze currently available technologies for learning. Web there are 4 modules in this course. Web uvm layered sequences this session shows how to create a virtual sequence, which controls the execution of other sequences and how to model.Universal Verification Methodology SoC Labs

System and Functional Verification Using UVM (Universal Verification

Universal Verification Methodology (UVM) Mentor Graphics

UVM the Universal Verification Methodology, moving to deployment

Universal Verification Methodology Doulos Uvm Golden Reference Guide

Universal Verification Methodology Doulos Uvm Golden Reference Guide

UVM the Universal Verification Methodology, moving to deployment

A Practical Guide to Adopting the Universal Verification Methodology

Universal Verification Methodology (UVM) 1.2 User’s Guide — uvm_python

UVM Environment Components Universal Verification Methodology

Web Universal Verification Methodology (Uvm) Is The Industry Standard Verification Methodology For Verification Using Systemverilog (Sv).

Web The Course Will Discuss The Fundamentals Of The Universal Verification Methodology.

The Uvm Class Library Provides The Basic Building Blocks For Creating Verification Data And Components.

In This Session, You Will Learn What The Uvm Framework Is, The Functionality It Provides, Its Testbench Architecture, And Available Documentation And.

Related Post: